SystemVerilog Shift 12 Bits Left: A Comprehensive Guide

Understanding the concept of shifting bits in programming is crucial, especially in the realm of digital design and verification. SystemVerilog, a hardware description language, provides a rich set of operations for bit manipulation. One such operation is the left shift, which can be particularly useful when dealing with binary numbers. In this article, we will delve into the specifics of shifting 12 bits left in SystemVerilog, exploring its applications, syntax, and best practices.

Understanding Bit Shifting

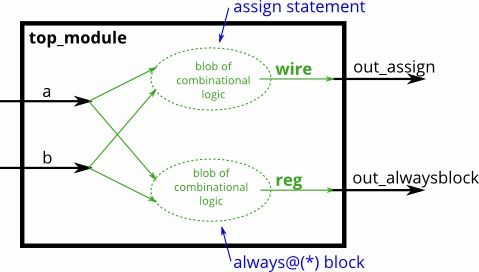

Bit shifting is a fundamental operation in computer science, allowing us to manipulate binary numbers efficiently. When we shift bits to the left, we multiply the number by 2 for each position shifted. Conversely, shifting bits to the right divides the number by 2 for each position shifted. In SystemVerilog, the left shift operation is denoted by the `<<` operator.

Shifting 12 Bits Left in SystemVerilog

Now, let’s focus on shifting 12 bits left in SystemVerilog. This operation is particularly useful when working with binary numbers that require a specific bit pattern. For instance, in digital design, we often need to align bits or create specific bit patterns for various purposes. Here’s how you can perform a 12-bit left shift in SystemVerilog:

reg [11:0] data;data = data << 12;

In this example, we declare a 12-bit register named `data`. By using the `<<` operator, we shift the bits in `data` 12 positions to the left. The resulting value is stored back in the `data` register.

Applications of 12-bit Left Shift

Shifting 12 bits left in SystemVerilog has various applications, some of which are:

| Application | Description |

|---|---|

| Bit Alignment | Aligning bits in a binary number to a specific position, making it easier to manipulate or extract specific bits. |

| Bit Pattern Creation | Creating specific bit patterns for various purposes, such as generating test vectors or implementing algorithms. |

| Binary Multiplication | Multiplying binary numbers by shifting and adding, which is a common technique in digital design. |

Syntax and Best Practices

When performing a 12-bit left shift in SystemVerilog, it's essential to follow the correct syntax and best practices. Here are some key points to consider:

- Register Size: Ensure that the register size is at least 12 bits to accommodate the shift operation.

- Operator Precedence: Remember that the left shift operator has higher precedence than the addition and subtraction operators. Use parentheses to group expressions if necessary.

- Bit Extension: When shifting bits, the leftmost bit is discarded, and zeros are filled in from the right. Be aware of this behavior when working with different bit widths.

Conclusion

Shifting 12 bits left in SystemVerilog is a valuable operation that can be used for various purposes in digital design and verification. By understanding the concept of bit shifting and following the correct syntax, you can manipulate binary numbers efficiently and achieve your desired results. This article has provided a comprehensive guide to performing a 12-bit left shift in SystemVerilog, covering its applications, syntax, and best practices.